# Abschlussbericht Projekt VoLiFa2020 – ("Volladaptive <u>Li</u>chtverteilung für eine intelligente, effiziente und sichere <u>Fa</u>hrzeugbeleuchtung")

Ersteller SCHWEIZER Electronic AG Jue Chen

Förderkennzeichen: 13N13046

### <u>Inhaltsverzeichnis</u>

| ABSCHLUSSBERICHT PROJEKT VOLIFA2020 – ("VOLLADAPTIVE<br>LICHTVERTEILUNG FÜR EINE INTELLIGENTE, EFFIZIENTE UND SICHERE<br>FAHRZEUGBELEUCHTUNG") | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| TEIL I – KURZE DARSTELLUNG DES PROJEKTES VOLIFA2020                                                                                            |    |

| Aufgabenstellung                                                                                                                               | 2  |

| Voraussetzungen                                                                                                                                | 2  |

| Planung und Ablauf des Projektes                                                                                                               | 3  |

| Stand der Wissenschaft und Technik (bezogen auf das Teilvorhaben)                                                                              | 4  |

| Zusammenarbeit mit anderen Stellen                                                                                                             | 4  |

| TEIL II – EINGEHENDE DARSTELLUNG PROJEKT VOLIFA2020                                                                                            | 5  |

| Demonstratoren LCD und LED Board in Cu-Inlay und Flex Technologie                                                                              | 5  |

| Auswahl AVTs für den Die Attach Prozess                                                                                                        | 9  |

| Auswahl Die Attach Prozess und die Verwendung von Underfilling - Material                                                                      | 11 |

| Leiterplatte für Vorfeldbeleuchtung mit Logik Embedding und Inlay Technologie                                                                  | 12 |

| Zusammenfassung Leiterplatter mit Logik-Embedding und Inlay Technologie                                                                        | 16 |

| Prüfnorm, Testkonzept und Zuverlässigkeitsuntersuchung von IC embedded Leiterplatte                                                            | 16 |

### Teil I – Kurze Darstellung des Projektes VoLiFa2020

#### Aufgabenstellung

Die Aufgabe des gesamten Projektziels von VoLiFa2020 war die Entwicklung eines intelligenten, volladaptiven Beleuchtungssystems auf Basis einer Halbleiter-Lichtquelle (LED) mit einem integrierten Flüssigkristall-Display (LCD) als Blendenelement. Durch Einsatz von LED als Lichtquelle mit Kombination der einzelsteuerbare Pixel von LCD mit hoher Auslösung ermöglicht das Scheinwerfersystem, dass ein maßgeschneidertes Licht hochdynamisch für jede Fahrsituation auf der Straße zu projizieren und ohne andere Verkehrsteilnehmer zu blenden.

Eine wichtige Voraussetzung ist dafür, alle notwendige Komponente, insbesondere die Elektronik vom hoch komplexen System mit Ansicht der Performance, Zuverlässigkeit, Lebensdauer und Umgebungsbedingung in einem begrenzten Raum einzubauen. Um diese Anforderung zu erfüllen stellt die Entwicklung neuartiger Leiterplatte zur Bestückung elektronischen Bauteilen eine zentrale Aufgabe für das Teilprojekt.

Die Aufgabe des Teilprojektes war die Entwicklung einer neuartigen Leiterplatte mit den Anforderungen, einerseits ein optimales Thermomanagement wegen der hohen Leistungsdichte im System, zum großen Teil wegen der hohen Verlustleistung von LEDs und andererseits die Miniaturisierung wegen des begrenzten Bauraums. SCHWEIZER verfügt in seinem Technologie Portfolio verschiedene innovative Leiterplattenlösungen, was sowohl für die Anwendungen von hoch Wärme und hohe Ströme, z.B. Inlay Board, Power Embedding p² Pack®, als auch für Miniaturisierung bzw. Logic Embedding i² Board®, zum Thema entsprechen.

Das Ziel von SCHWEIZER war die Erforschung eines Embedding Konzeptes, das sowohl Logik- als auch Leistungskomponenten und deren Kommunikation abdeckt. Das Weitere muss die Einbettung (Embedding) von ungehäusten Halbleiterbausteinen mit geeigneter AVT Technologie geforscht werden. Die Grundlage der Embedding Technologie basiert auf dem i² Board® ggf. dem p² Pack®.

Am Ende des Projektes sollte ein Demonstrator in hochkompakter Bauweise auf Leiterplattenbasis zur Verfügung stehen.

### Voraussetzungen

Die Partner des VoLiFa2020 Projektes repräsentierten die komplette Wertschöpfungskette eines Hauptscheinwerfers, ausgehend von den Halbleiter (Elmos Semiconductor AG) und LCD-Materiallieferanten (Merk KGaA) bis zum Hersteller von gesamtem Scheinwerfersystem (Hella AG) und dem OEM Unternehmen (Porsche AG). Damit wurden die Voraussetzungen geschaffen, eine neue Technologie möglichst breit aufzustellen und Markteintrittshürden zukünftig zu verringern.

Die Grundlage der i² Board® Technologie stellt ein strukturierter Interposer als Verdrahtungsschnittstelle zwischen Halbleiterelementen (IC) und Leiterplatten dar, auf den die ICs und falls notwendig, auch passive Bauelementen direkt bestückt werden können. Die Technologie weist verschiedene Vorteile auf. Durch Ansatz vom Interposer bietet die Leiterplatte neben den beiden Außenebenen eine zusätzliche Bestückungsebene, was die Miniaturisierung der Leiterplatten ermöglicht. Die Anbindung der Halbleiter auf Interposer erfolgt durch Chip Bestückungsprozess "Die Attach". Vorher wird auf dem Halbleiter eine "englisch sogenannte Aufbauund Verbindungstechnick interconnection (AVT) technology" aufgebracht. Der Chip Bestückungsprozess und das Aufbringen von AVT werden im Projekt durch den Unterlieferanten durchgeführt. Nach dem Einbettungsprozess, nämlich Leiterplattenlaminierungsprozess, folgt die weitere Fertigung wie eine normale Multilayerleiterplatte. Durch Direkteinbettung von ungehäuste ICs ermöglicht kompakter

Aufbau wegen kürzerer Leitungswege und inhärente Abschirmungslage, wodurch eine verbesserte elektrische Performance erreicht werden kann. Neben der Robustheit sparen zusätzlich die Gehäusekosten.

Mit der zunehmenden Komplexität der Elektronik im Auto sollen in Zukunft mehr Bedarfe vom Embedding steigen. Diese Fertigungstechnologie soll den Vorsprung, von deutschen Anwendern und Nutzern in der Automotivindustrie, weiter ausbauen und die technischen Potentiale am Standort Deutschland sichern und nutzbar machen.

### Planung und Ablauf des Projektes

Die gesamte Arbeitsplanung gliederte sich im Wesentlichen nach den Arbeitspaketen. Zum Beginn des Projektes leiten der Endanwender, Porsche AG, mit Projektpartner Uni Paderborn in AP1 die Lichtfunktionen von neuartigem adaptivem Scheinwerfersystem aus realen Fahrsituationen ab. Damit wurde in AP2 das Lastenheft inklusiv alle Anforderungen und Spezifikationen gemeinsam durch das Projektkonsortium definiert. In nachkommender Phase wurde in AP3 das optische System unter der Leitung von Hella entworfen. Während dieser Phase wurde zwischen Hella und SCHWEIZER verschiedene Leiterplattenansätze inklusiv eingehende Thermal Management zur Anbindung von LED konzipiert, welche wieder als Grundlage bei der Festlegung des optischen Systems beeinflussen wurde.

Nach der Festlegung gesamter Systemarchitektur wurden alle Anforderungen zum elektronischen System abgeleitet. Daraus definiert die Randbedingungen, wie z.B. der Bauraum, die geschätzte Verlustleistung, das gesamte Entwärmungskonzept und die Anordnung aller elektronischen Funktionsgruppe, was bei der Suche der geeigneten Leiterplattenlösung sowie der Entwicklung des Embedding Ansatzes entscheidet ist.

Ausgehend von dem elektronischen Systementwurf und dem Design der mechanischen Konstruktion gilt es die bestehenden Bauteile und das Bauraum auf ihre Eignung für das Embedding zu analysieren. Aufbauend auf dieser Analyse sind mit Projektpartner Hella beschlossen, dass jeweils die Hauptleiterplatte inklusiv LED und Ansteuerungselektronik ohne und das Vorfeldmodul mit Logic Embedding Technologie, i² Board®, anzuwenden.

Während der Entwicklung der Hauptleiterplatte wurde eine Testleiterplatte zur Verifizierung des ausgesuchten Thermal Management Konzeptes hergestellt. Die wurde bei Hella mit Matrix-LEDs bestückt und in einem Tischdemonstrator zum Test der optischen Funktion aufgebaut. Nach der Erprobe der Testleiterplatte wurde das technische Design für Hauptleiterplatte festgelegt. Die Technologie von Cu-Inlay wird neuartig mit der FR4-Flex Technologie kombiniert, damit die Kompaktheit, die 3D Anpassung zum Kühlkörper und gleichzeitig die hervorragende lokale Entwärmungsfähigkeit in einer Leiterplatte realisiert wurden.

Parallel dazu wurde bei SCHWEIZER die weitere Entwicklung des Embeddings von Halbleiterbausteine gestartet. Verschiedene AVT (Aufbau- und Verbindungstechnik) Technologien zur Anbindung des Halbleitermaterials auf Interposer wurden analysiert. Anhand der durch Chip definierten Randbedingungen, wie Chip Abmessung, Pads Geometrie, Pitch-Size wurde Cu-Pillar als Verbindungstruktur zwischen Chip und Interposer ausgewählt. Da dieser zusätzliche Umarbeitungsprozess nicht durch einen Projektpartner abgedeckt war, wurde ein geeigneter Unterlieferant gesucht und beauftragt. Das Layout mit Embedding Technologie für das Vorfeldmodul werden mit Hilfe eines externen Layoutdesigners gemeinsam durch Hella, Elmos und SCHWEIZER erstellt. Die Design-Guidelines für das Embedding wurde im Vorfeld definiert und berücksichtigt. Sobald der Chip bzw. Wafer mit Cu-Pillar bearbeitet wurden, werden der Chip hochpräzise auf dem Interposer bestückt. Dieser so genannt Flip Chip Prozess wurde bei einem anderen Unterlieferant durchgeführt. Am Ende wurde die Leiterplatte mit Embedding für das Vorfeldmodul bei SCHWEIZER fertig gebaut. Die gefertigten Leiterplatten wurden an Hella geliefert und bei ihm mit allen elektronischen, optischen und mechanischen Elementen in einem Demonstrator zusammengebaut.

### Stand der Wissenschaft und Technik (bezogen auf das Teilvorhaben)

Die Technologie zur direkten Einbettung von ungehäusten Halbleiterbauelementen (engl. bare die) im organischen Substrat wird bereits in 3C-Markt (Computer, Communication und Consumer Electronic) weit entwickelt und angewendet. Verwandt zu SCHWEIZER i² Board® Technologie werden mehrere bare dies zusammen gestapelt oder nebeneinander auf einem Silizium oder Glas Interposer gebracht und anschließend im Epoxyharz basierten Matrix verkapselt, um Platz zu sparen und die Signalwege zwischen Einzel-ICs zu verkürzen. Dagegen wird in der Automotivindustrie aufgrund der hohen Anforderung an der Zuverlässigkeit und der Robustheit bisher nicht verbreitet. Heutzutage sind im Auto eingebaute elektronische Bauteile meisten mit Gehäuse diskret nebeneinander auf der Leiterplatte platziert. Durch die Entwicklung von zunehmenden innovativen Funktionen, wie z.B. in VoLiFa2020 Projekt zu entwickelnder intelligenten Fahrzeugbeleuchtungssystem, wird die elektronische Hardware komplexer und der verfügbare Bauraum für Leiterplatte immer enger. Automobilindustrie ist dafür herausgefordert, neuartige Lösungsansätze finden zu müssen. Bisher in früheren Forschungsprojekten wurden reine Logik-ICs in verschiedenen Technologiedemonstratoren eingebettet und erprobt. Bei dem Fall für Leistungselektronik wurden reine Leistungshalbleiter wie MOSFETs oder IGBTs durch p2 Pack® Technologie in die Leiterplatte eingebettet. Die Einsatzmöglichkeit für die Anforderungen des VoLiFa2020 Projekts wie z.B. die Miniaturisierung und das optimales thermische Management wegen der LEDs mit hoch Leistungsdichte noch nicht geprüft. Außerdem wegen extremer Einsatzbedingung wie Temperatur und Dauerfeuchtigkeit müssen die Fertigungsprozesse für das Embedding neu entwickelt werden.

#### Zusammenarbeit mit anderen Stellen

Nur durch die enge Kooperation und das spezialisierte Know-how der Partner aus Industrie und Forschung konnte das innovative Aufbaukonzept für den finalen Leiterplatten Embedding Demonstrator realisiert werden. Der LED Treiber-IC wurden durch Elmos entwickelt und bereitgestellt. Die Waferumarbeit und der Flip Chip Bestückungsprozess wurde jeweils durch einen Spezialist in der Halbleiter-Backend-Industrie als Unterlieferant übernommen und durchgeführt. Hella trägt das bei, dass mit SCHWEIZER das Thermal Management Konzept und das Leiterplattenlayout für Hauptleiterplatte zu erstellen. Für Vorfeldmodul mit Embedding Technologie wurde Elmos den Schaltplan entworfen und gemeinsam mit SCHWEIZER das Layout realisiert.

### Teil II – Eingehende Darstellung Projekt VoLiFa2020

### Demonstratoren LCD und LED Board mit Cu-Inlay und Flex Technologie

Ausgehend für LCD und LED adaptivem Modul stellt eine der zentralen Aufgabe, wie die hochström LED-Chips auf Leiterplatte zu bestücken und die Verlustleistung effizient durch die Leiterplatte zum Kühlkörper wegzuführen und die Beschädigung des LED-Chips wegen der Überhitze, nämlich Betrieb über Tj,max (maximal junction temperature), zu vermeiden. Vorgegeben wurde es durch die Anforderung von gesamtem Lichtstrom aus AP3, dass insgesamt 25 hochströme LEDs mit jeweils maximal 3A Strom in adaptivem Modul im Einsatz zu kommen. Weitere Informationen für die thermische Auslegung Matrix LED Leiterplatte wurden ermittelt.

| Anzahl LED                                | 25       | Stück |

|-------------------------------------------|----------|-------|

| Vorwärtsspannung $V_f$                    | 2,5~3,8  | V     |

| Max. Strom $I_f$                          | 3        | Α     |

| Max. Verlustleistung pro LED (geschätzt)  | 5~7      | W     |

| Tj,max (maximal Junction temperature) LED | 150      | °C    |

| Ansatztemperatur                          | -40 ~125 | °C    |

| Padsabstand einzelne LEDs (pitch size)    | 350      | μm    |

Tabelle 1: Kenndaten von LED Matrix und verwendeter LED Chip

Da am Anfang des Projekt der elektrische Schaltplan noch offen war, wurde es angenommen, dass bei der elektrischen Verschaltung eine Isolationsschicht zum Kühlkörper benötig. Verschiedene Leiterplattenansätze zur Anbindung von LED Chips inklusiv eingehende Entwärmungskonzepte wurden zwischen Hella und SCHWEIZER konzipiert. Die wesentlichen Aufbauvarianten werden in Abb. 1 dargestellt. Hinsichtlich der thermischen Performance, der fein Pitch Fähigkeit wegen des LED Padsabstands, der Flexibilität bei der Verschaltung aller 25 LEDs, der Kosten und der Herstellbarkeit von Leiterplatte wurden alle Aufbauvarianten bewertet (Tabelle 1).

(Die Abbildung wurde aus Geheimhaltungsgründen entnommen)

Abbildung 1 Grundaufbauvarianten der Leiterplatte für LCD und LED adaptiv Modul mit a) IMS (isolated metal substrate), b) Cu Inlay c) dick Cu Technologie

(Die Tabelle wurde aus Geheimhaltungsgründen entnommen)

#### **Tabelle 2 Bewertung aller Aufbauvarianten für LED Leiterplatte**

Nachhinein wurden die LED Chips mit integriertem Thermalpad für das Projekt ausgewählt. Die elektrische Ansteuerung wurde so gestalten, dass die Kathode aller 25 LEDs gemeinsam mit Thermopad und auf GND zum Kühlkörper verbunden wurde (common cathode). Die Verdrahtung zur LED-Anode wurde durch die oberste Cu-Lage realisiert. Daher war die zusätzliche Isolationslage zum Kühlkörper nicht nötig. Auf diesen Grund wurde die Lösung mit durchgängigem Cu-Inlay mit einer symmetrischen Aufbauweise entschieden. Eine thermische Berechnung in Bezug auf einem einzelnen LED ohne Berücksichtigung von Lotverbindung und Verbindung zum Kühlkörper wurde durchgeführt.

(Die Abbildung wurde aus Geheimhaltungsgründen entnommen)

### Abbildung 2 Festgelegter Aufbau für Matrix LED Leiterplatte und die thermische Berechnung ohne Berücksichtigung von Lot- und TIM Verbindung

Basiert auf dieser Aufbauvariante wurde eine Testleiterplatte zur Erprobung des Fertigungsprozesses und zur Verifizierung der thermischen Performance hergestellt. 1mm dick massive Cu Inlay wurde für die optimale Entwärmung in die Leiterplatte eingebettet. Micro-Vias Felder wurden verwendet um Wärme effizient aus LEDs in Cu-Inlay zu führen. Um eine hohe Wärmeleitung zu erreichen wurden alle Vias mit Cu durch speziellen Galvank Prozess (Copper Via Filling) gefüllt. Einige Proben wurden bei SCHWEIZER anschließend dreimal mit einem Pb frei Temperaturprofil durch die Reflowofen belastet. Alle Testproben zeigen keine Auffälligkeit zu Delaminationen oder ähnlichen Defekten. Die restlichen Teile wurden beim Partner Hella für Aufbau eines Tischdemonstrators verwendet. Die Lichtfunktion wurde damit vorab getestet.

(Die Abbildung wurde aus Geheimhaltungsgründen entnommen)

# Abbildung 3 Cu Inlay (oben links), Draufsicht gefertigter Musterleiterplatte, LED Bestückseite (oben rechts), Schliffbilder einer Musterleiterplatte (mitte) und einzelner micro-Vias (unten) nach 3x Reflow Belastung

Anderes Projektziel von Arbeitspaket Elektronik war, dass den potentiellen Bauraummangel zunehmender Elektronike und Komplexität durch Embedding wegen Halbleiterbausteinen bzw. passiven Bauteilen zu lösen. Nach der Festlegung des optischen der Systemarchitektur wurde Systems und von Projektpartner Hella Konstruktionsvorschlag entworfen. Die Hauptleiterplatte, welche die LED Lichtquelle und die Ansteuerungselektronik drauf bestückt werden sollen, könnte durch speziellen gestalteten Kühlkörper horizontal im Scheinwerfer eingebaut werden. Dadurch ist der Scheinwerfer genügend Einbauplatz für Leiterplatte vorhanden. Gemeinsam mit dem Partner Hella wurde eine Platzstudie anhand des Schaltplanes und der Bauteilgröße für die Platzierung aller Bauelemente im oder auf dem Leiterplatte durchgeführt. Nach den Kriterien von Schnittstelle. Bauraumverfügbarkeit, Realisierbarkeit des Layouts und thermischer Performance wurden verschiedene Platzierung bzw. Embedding Lösungen ausgewertet. Schließlich wurde gemeinsam für Standardlösung ohne Embedding, nämlich Bestückung von diskreten Bauteilen auf der Leiterplatte, entschieden.

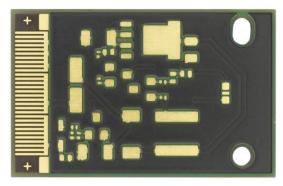

(Die Abbildung wurde aus Geheimhaltungsgründen entnommen)

Nach der Festlegung des Schaltungsdesigns für komplettes elektronisches System wurde der restliche Lagenaufbau für ECU-Bereich entworfen. Ein 8 lagriger Multi-Layer mit verschiedenen Via-Technologien, z.B. buried via (BU), micro via (MIC), blind via (Blind), PTH (plated through hole) und mit Plugin-Material gefülltem Via erlaubten eine flexible vertikale Verbindung, eine separate Leitungsführung mit unterschiedlichen Stromtragfähigkeiten und der EMV Anforderungen. Durch Einsatz von FR4-Flex Technologie wurde das ECU-Bereich und LED Bereich in einer Leiterplatte vereinigt. Dadurch bietet diese Lösung verschiedene Vorteile wie die Langzeitstabilität, der geringeren Platzbedarf durch direkte Leiterbahnverbindung ohne zusätzliche Stecker und die 3D-Anpassungsfähigkeit an der Bauform von Kühlkörper. Abbildung 4 zeigt den Lagenaufbau der Leitplatte von LED LCD adaptiv Modul.

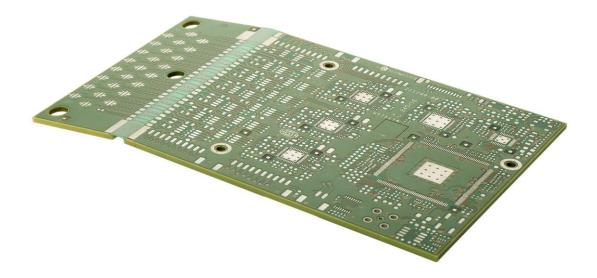

Abbildung 5 Fertige Leiterplatte für LED und LCD adaptives Modul

(Abbildung wurde aus Geheimhaltungsgründen entnommen)

Abbildung 6 Schliffuntersuchung: a) Blind und buried Via; b) plugged-PTH c) microvia; d) Cu-Inlay mit micro-via

Die Potentiale sind umfangreich:

- Miniaturisierung: 25 x Hochstrom LEDs Matrix, LED Treiber und ECU-Einheit in EINER Leiterplatte

- 3D einbaufähig durch FR4 Flex Technologie: definiert Biegewinkel 10°

- Einsatz 1,5mm dick Cu Inlay für Thermomanagement

- 8 Lage Multilayer im Logikbereich

- Verschieden Via Technologien: Micro-via, blind via, buried via, PTH, plugged-PTH

#### Auswahl AVTs für den Die Attach Prozess

Indirekte Chip-Kontaktierung mit einem Interposer ist die Kerntechnologie vom Logik Embedding mittels i² Board® Technologie. Daraus steht die geeignete AVT(Aufbau und Verbindungstechnik) Technologie eine wichtige Rolle zur Anbindung vom nackten Chip und Interposer. Heutzutage werden im Halbleiterbackendindustrie verschiedene AVT-Technologien für Flip Chip Bestückung zur Kontaktierung von bare entwickelt.

Bei einer Pitch Größe >150µm kommen meisten Lötkugeln (engl. solder bump) zum Einsatz. Bei feinem Pad-Pitch von Chip sind dagegen andere AVTs notwendig. Ein sogenannt Cu-Pillars Bump besteht aus einer Cu Säule und Lotkappe, kann z.B. bis zum 40µm fein Pitch erreichen. Weitere alternative Technologie gehört das Stud Bump, wobei bei der Herstellung wegen des sequenziellen Aufbringprozesses wesentlich aufwendiger ist. In Tabelle 3 wird mögliche AVTs für den Einsatz zum Embedding dargestellt.

|             | Pitch | Prozesszeit             | geeignete Flip Chip Technologie                                                                 |

|-------------|-------|-------------------------|-------------------------------------------------------------------------------------------------|

| Stud bump   | fein  | langsam,<br>sequenziell | non-conductive adhesive(NCA) Conductive adhesive Thermo-Compression bonding Thermosonic bonding |

| Solder bump | grob  | schnell, batch          | Reflow Löten (mass reflow)                                                                      |

| Cu Pillar   | fein  | schnell, batch          | Reflow Löten (mass reflow) Thermo-Compression bonding                                           |

Tabelle 3 verschiedene AVTs mit entsprechende Flip Chip Technologie Konfigurationen

Am Anfang des Projekts wurde vorgesehen, dass der LED Treiber-IC von Partner Elmos für Logik Embedding anzuwenden, weil dieser IC die größte Package-Dimension aufwies und die meisten I/Os besitzt. Durch Embedding von diesem aktiven Bauelement hat das größte

Potential, den meisten Platz zu sparen und den gesamten Signalweg zu verkürzen. So wurden im Vorfeld die Wafer/Chip Informationen, welche für die Auswahl geeigneter AVT-und Flipchip-Technologie relevant sind, ermittelt.

Folgende Wafer/Chip-Spezifikationen wurde durch Partner Elmos zur Verfügung gestellt:

Wafer Material: Silizium

Wafer Size: 8 Zoll, entspricht 200mm Durchmesser Wafer Dicke: 725µm (im ungedünnten Zustand)

Min. Pads Pitch Size: 119µm

Pads Größe: 70µm Pads Metallisierung: AlSi Aktive Halbleiterlage: <10nm

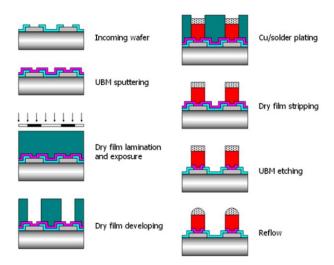

Wegen der Anforderung an feinem Pitch von ICs und des Vorteils von Batchprozess wurde Cu-Pillars als die beste geeignete Lösung ausgewählt. Da beim Cu-Pillar Herstellungsprozess automatisch eine so genannte UBM (under bump metalization) auf dem Pads beschichtet wird, kann der Chip mit der ursprünglichen Padsmetallisierung von AlSi direkt verarbeitet werden. Abbildung 7 zeigt schematisch einen typischen Herstellungsprozess von Cu-Pillar.

#### Abbildung 7 Schematische Darstellung von Cu-Pillar Herstellungsprozess

Für den Herstellungsprozess von Cu Pillar wurde der Halbleiter als Waferform verwendet. Nach engerer Abstimmung mit Unterlieferant wurde eine zusätzliche Repassivierung von Polyamid (PI) eingesetzt. Diese PI Schicht diente als Puffer zur Absorption von mechanischen Spannungen zwischen Halbleitermaterial und Cu-Pillar Struktur und verbessert sich damit die Zuverlässigkeit. Der Standard-Repassivierungsprozess beim Halbleiterhersteller wurde damit erspart. Folgende Änderungen zum Anlieferzustand des Wafers wurden für die Waferumarbeitung u.U. das Aufbringen von Cu Pillar vorgenommen.

|                       | Standard IC      | Für Embedding    |

|-----------------------|------------------|------------------|

| Gehäuse               | Ja (QFN)         | ohne             |

| Wafer/Chip Dicke [µm] | gedünnt zu 250µm | ungedünnt 725µm* |

| Repassivierung        | PI               | ohne**           |

| Wafertest             | Ja               | nein***          |

<sup>\*:</sup> Wafer wird erst nach cu Pillar Prozess auf 250µm gedünnt

<sup>\*\*:</sup> Wird bei Cu-Pillar Prozess aufgebracht

<sup>\*\*\*:</sup> Testen nach der Bestückung, vorgesehen beim Partner Elmos

# Tabelle 4 Vergleich der Anlieferzustände von Halbleitern zwischen Standard Anwendung und Embeddinglösung mit Wafer Umarbeitungsprozess (Cu-Pillar Prozess)

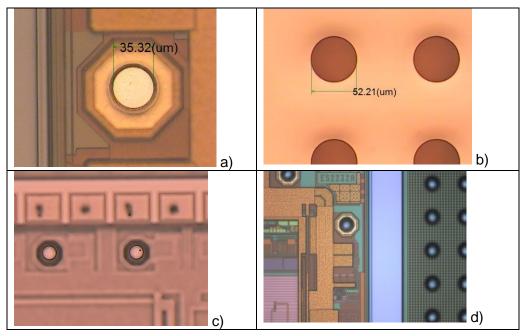

Abbildung 8 zeigt die mikroskopischen Aufnahmen während des Fertigungsprozesses von Cu-Pillar.

Abbildung 8 Mikroskopische Aufnahmen: a) nach PI Repassivierung mit Öffnung; b) nach Fotolithografieprozess für Galvanik Cu/Solder; c) nach Galvanik von Cu/Solder Material und d) nach Reflow Formen vom Soldermaterial

### Auswahl Die Attach Prozess und die Verwendung von Underfilling - Material

Std Mass Reflow Bonding of FC

Thermocompression FC Bonding for Fine Pitch

### Abbildung 9 Vergleich Flipchip Technologien: Reflow-Löten und Thermokompression Bonding

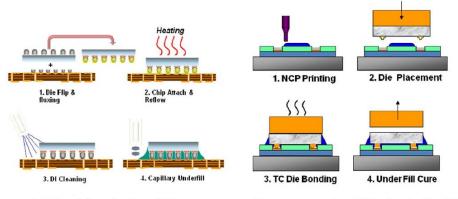

Beim Die Attach Prozess mit Cu-Pillar sind beide Flipchip Technologien anwendbar, nämlich Reflow-Löten und Thermokompressionsbonding. Der Prozessablauf der beiden Technologien wird in Abbildung 9 schematisch gezeigt. Beim Reflow-Löten wird Chip zuerst

auf einem Substrat gelötet und dann wird der Raum zwischen Chip und Substrat mit einem so genannten Underfilling Material durch kapillares Effekt unterfüllt. Beim Thermokompressionsbonding dagegen wird das Underfilling Material zuerst auf dem Substrat gebracht. Dann wird der Chip unter der Temperatur und dem Druck bestückt. Durch Einsatz von Underfilling Material verlagert sich die mechanische Spannung, die durch unterschiedliche CTE (Coefficient of Thermal Expansion)-Werte zwischen dem Halbleitermaterial und dem organischen Material verursacht wird, von der Lötstelle nach gesamter Bondfläche von Chip. Die Gefahr von Rissbildung in der Lötstelle wird somit reduziert und die Robustheit des Aufbaues wird verbessert.

Reflow-Löten wurde als Die Attach Prozess für das Projekt ausgewählt. Das bietet zusätzlich die Option, andere Bauelemente in einem Reflow Vorgang auf einem Interposer zu löten, was ein entscheidendes Kriterium für die Embedding Anwendung im VoLiFa2020 Projekt ist. Zudem ist Reflow-Löten wegen derer Batchprozesseigenschaft viel kosteffizienter im Gegensatz zu Thermokompressionsbonding, was für die künftige Serienherstellung relevant wäre.

(Dieser Abschnitt wurde aus Geheimhaltungsgründen entnommen)

### Leiterplatte für Vorfeldbeleuchtung mit Logik Embedding und Inlay Technologie

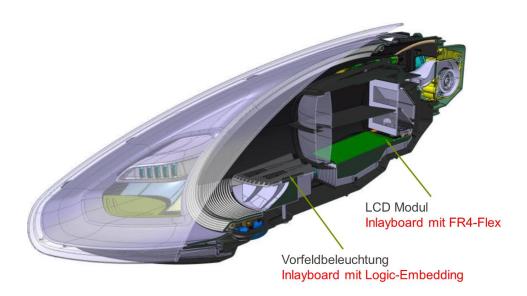

#### Abbildung 10 Leiterplatte in VoLiFa2020 Schweinwerfer

Neben dem LED LCD adaptiven Modul ist für die gesamte Lichtfunktion im Projekt eine zusätzliche so genannte Vorfeldbeleuchtung zur Ausleuchtung des Nähfeldbereichs nötig. Wegen der Einbauweise ist es nötig, die Leiterplatte kompakt wie möglich zu gestalten. Ein Hochstrom-LED mit der Ansteuerungselektronik, wie z.B. die Schaltung für PWM Dimming, Temperatur Überwachung durch einen Sensor zu schützen vor Übertemperatur und die Stromversorgung sind in diesem Modul zu integrieren. Da der komplette Schaltungsblock alle benötige Elektronik beinhält, sind lediglich nur 3 Anschlüsse für die Stromversorgung

aus Batterie, das LED PWM Dimmingsignal und PGND nötig. Die wurden durch ein Flex-Kabel mittels ACF (anisotropic conductive film) Bonding Technik ohne Verwendung von Stecker mit Hauptleiterplatte verbindet.

Folgende Randbedingungen wurden von Hella für Vorfeldbeleuchtung vorgegeben:

Dimension (Leiterplatte): 32mm x 15mm Betriebstemperatur: -40°C ~ 85°C 1 Hochstrom LED: I<sub>f</sub> max 3A, V<sub>f</sub> 2~5V

3 PINs: Vbat, PGND, PWM

Temperaturüberwachung von LED

(Diese Abbildung wurde aus Geheimhaltungsgründen entnommen)

### Abbildung 11: Leiterplatte für Vorfeldbeleuchtung: Dimension und verfügbarer Platz zur Bestückung von Bauteilen

Der Schaltplan zur Umsetzung der angeforderten Funktion wurde durch den Partner Elmos entworfen. Eine zugehörte Bauteilliste wurde definiert. Basierend auf dieser Stückliste wurde eine Platzstudie durchgeführt. Nach grober Berechnung wurde festgestellt, dass die gesamte Footprint aller zu bestückenden Bauteilen ungefähr gleich groß wie die vorgegebene Leiterplattendimension. Basiert auf dieser Einschätzung ist das Embedding von Bauelementen in die Leiterplatte zwingend notwendig. Abbildung 11 zeigt die Dimension der Leiterplatte und die mögliche Bestückungsfläche auf der Leiterplatte.

(Diese Abbildung wurde aus Geheimhaltungsgründen entnommen)

### Abbildung 12 Bestückung- und Embedding-Konzept der Leiterplatte für die Vorfeldbeleuchtung

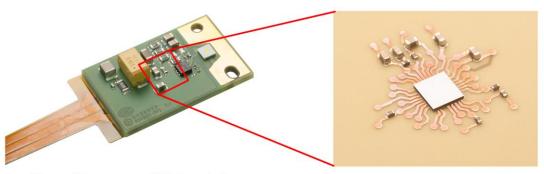

Ähnlich wie beim LED-LCD-adaptiv Modul wurde ein dickes Cu-Inlay für die Thermomanagement eingesetzt. LED Chip sollte direkt auf den Inlay-Bereich bestückt werden und die Wärme durch Micro-Vias über Inlay zum Kühlkörper abgeführt werden. Zur Bauteilauswahl für Embedding wurden alle Bauteile nach ihrer Geometrie analysiert und klassifiziert, wie sie zum Embedding geeignet sind. Aus vorher bereits erklärtem Grund Treiber IC als Embedding Kandidat ausgewählt. Verschiedene Embeddingskonzepte wurden etabliert. Mit i<sup>2</sup> Board® durch Interposer besteht die Möglichkeit, dass neben Logik IC weitere Bauelemente, sowohl Leistungselektronik (MOSFET) als auch die passive Bauelemente, gemeinsam drauf zu löten. Nach der Analyse von Schaltplan wurden weitere passive Devices (6 Widerstände, 5 Kondensatoren), die unmittelbar zu Treiber-IC verbündet sind, auch zum Embedding ausgewählt. Dieses Hybrid Embedding Konzept bietet das Vorteil, dass eine kleine enge zusammengehörte Schaltungsgruppe direkt auf einer Ebene (Interposer) ohne zusätzliche Umwege durch vertikale Verdrahtung von Vias zu verbinden. Dadurch bietet das Potential, die gesamte Leitungslänge zu verkürzen und die EMV Eigenschaft zu verbessern.

(Diese Abbildung wurde aus Geheimhaltungsgründen entnommen)

#### Abbildung 13 Schaltplan und Auswahl der Schaltungsgruppe zum Embedding

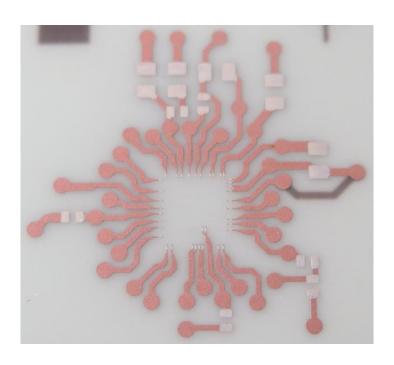

Das vollständige Leiterplattenlayout mit Embedding wurde durch SCHWEIZER und einen externen Layout-Designer mit enger Abstimmung von Partner Elmos gemeinsam erstellt. Der Interposer dient als zusätzliche Bestückungsebene in der Leiterplatte. LED Treiber IC von Partner Elmos und 11 passiv Bauelemente in SMD Bauform sollen drauf bestückt werden. Da wegen Waferumarbeitungsprozess die ICs in einem elektrisch ungetesteten Zustand im Waferform geliefert sind, wird der Test erst nach dem Chip Bestückung geplant. Nach Abstimmung mit Partner Elmos wurden zusätzliche Testpads im Layout eingebracht. Weitere kleine Layoutänderung wurde entsprechend vorgenommen. Abbildung 14 zeigt das Layout von Interposer und die Revision wegen Chip Test.

(Diese Abbildung wurde aus Geheimhaltungsgründen entnommen)

### Abbildung 14: Layout von Interposer mit darauf zu bestückenden Bauelementen, erste Version (links) und Revision wegen Chip Test

(Dieser Abschnitt wurde aus Geheimhaltungsgründen entnommen)

### Abbildung 15: Speziell oberflächenbehandelte Leitungszüge mit partieller Ag-Schicht auf dem Bondpad

(Dieser Abschnitt wurde aus Geheimhaltungsgründen entnommen)

- 32 mm x 20 mm, approx. 50% size reduction

- IC and 11 SMD embedded

- · 1.5mm copper Inlay

- · 3 external contacts

Abbildung 16 mit LED Treiber IC und passiven Bauelementen bestückter Interposer (rechtsoben), Oberseite einer bestückten Vorfeldleiterplatte mit Embedding (links) und das Schliffbild der Vorfeldleiterplatte (rechtsunten)

Nach Chip&SMD Bestückung wird der Interposer bei SCHWEIZER in die Leiterplatte eingebaut. Aus ästhetischem Grund wurde ein schwarzer Stopplack für die obere Seite verwendet. Nickel-Gold als die Endoberfläche wurde beschichtet. Durch das Embedding ist die Leiterplatte von außen gesehen sehr kompakt.

Abbildung 17 Gefertigte Leiterplatte mit Embedding und Inlay Technologie für Vorfeldbeleuchtung

### Zusammenfassung Leiterplatte mit Logik-Embedding und Inlay Technologie

- Miniaturisierung: Hochstrom LEDs und Ansteuerungselektronik in einer kleinen Leiterplatte

- Hybrid Embedding vom Logikhalbleiter und von passiven Bauelementen mittels i² Board®

- Cu-Pillar als AVT Technologie und Flipchip Bestückung mit Underfilling-Prozess für Die Attach Prozess

- Cu Inlay und Mikro Via Feld für Thermalmanagement

- Robustheit und Zuverlässigkeit von Leiterplatte mit Embedding wurde erfolgreich getestet

### Prüfnorm, Testkonzept und Zuverlässigkeitsuntersuchung von IC embedded Leiterplatte

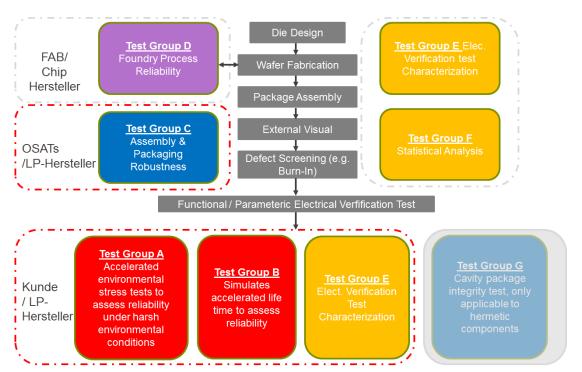

Abbildung 18 Aufteilung in Prüfgruppen nach AEC Q100 Norm und die mögliche Umsetzung durch jeweilige Partei für die IC embedded Leiterplatte

Für ICs embedded Leiterplatte gibt es bisher keine Norm, wo die Zuverlässigkeitsprüfung definiert ist. Es gibt lediglich die Normen aus der Leiterplattenindustrie und der Halbleiterindustrie, welche nur jeweils für Standardleiterplatte und für die gehäuste Halbleiter sind. Die werden als Grundlagen zur Erstellung Prüfkonzept für embedded Leiterplatte genommen.

- Leiterplatte: IPC 6012, 6016

- Halbleiter Bauelemente: AEC Q100

- Passive Bauelemente: AEC Q200

Nach Gegenüberstellung von Normen wird festgestellt, dass die Halbleiterteste "Test Group A" in AEC Q100 ähnliche Leiterplattenteste aus dem IPC Normen beinhalt. Die restliche Teste, wie "Foundry Process", "Assembly Process", usw. sollen durch die Teste von Chip Hersteller, OSATs und Kunden abgedeckt werden. Die genaue Klassifizierung muss in

Zukunft bei dem Fall der Serienproduktion mit allen Partnern gemeinsam definiert werden. Abbildung 18 zeigt die in AEC Q100 geforderte Teste in verschiedenen Gruppen und die möglichen Umsetzung durch jeweilige Partei.

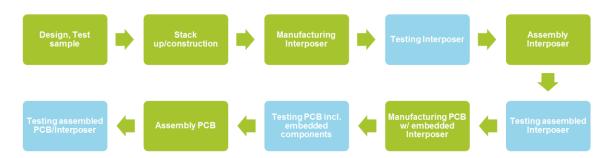

Aufgrund des Fertigungsablaufs von embedded Leiterplatte bietet i² Board® Technologie verschiedene Testmöglichkeiten nach jeweiligen Prozessabschnitten. Ein von SCHWEIZER vorgestelltes Testkonzept wird in Abbildung 19 dargestellt.

#### Abbildung 19 Testkozept für embedded Leiterplatte

Test vom Interposer wurde bereits in der Leiterplattenfertigung integriert. Nach der Leiterbahnstrukturierung werde Interposer durch einen so genannten AOI-Test (*automatic optical inspection*) automatisch visuell mit dem originalen Layout verglichen und die fehlerhaften Teile wurden aussortiert.

Nach dem Die Attach wurde der bestückte Interposer am Partner Elmos geliefert. Der elektrische Funktionstest wird dort durchgeführt. Ein Testadapter wurde dafür aufgebaut und der Signalabruf zum Chip wurde durch den Kontakt mittels Prüfnadeln zum Testpads auf dem Interposer realisiert.

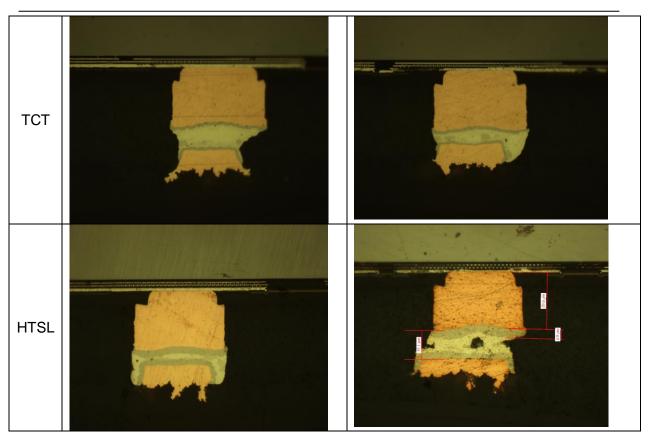

Nach der Fertigung wurden ein paar Leiterplatten mit eingebetteten Bauelementen als Testproben verwendet und bei SCHWEIZER unter Temperatur und Feuchtigkeit belastet, um die langzeitige Umweltbedingung bzw. den Lötprozess für die Endmontage zu simulieren. Drei Teste wurden aus den Normen von AEC Q100 und IPC 6012/6016 ausgewählt und die Testbedingungen wurden entsprechend nach der Projektanforderung angepasst.

| Testarten                            | Testbedingungen                        |

|--------------------------------------|----------------------------------------|

|                                      | Dauer der Ablagerung: 168 Stunden      |

| MSL3 (moisture sensitive level)      | Temperatur und Feuchtigkeit: 30°C/60%  |

|                                      | danach 3 x Reflow mit einem bleifreien |

|                                      | Reflow-Profil bis 260°C                |

| TCT (Thermal cycling test)           | Temperatur: -40°C~+125°C               |

|                                      | Zyklen: 1000                           |

| HTSL (High Temperature Storage Life) | Dauer der Ablagerung: 1000 Stunden     |

|                                      | Temperatur: 150°C                      |

#### Tabelle 5 Zuverlässigkeitsteste mit Vorfeldleiterplatten

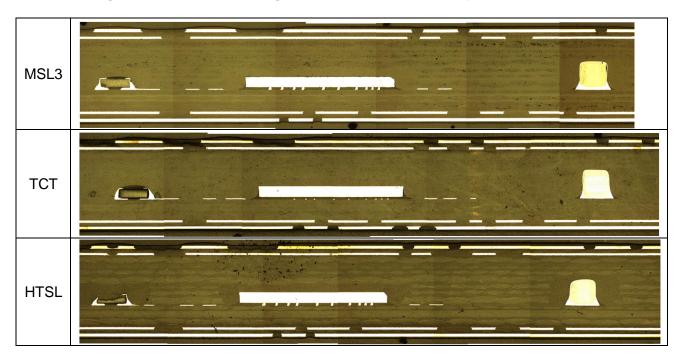

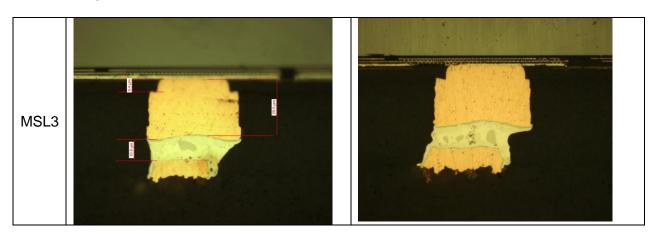

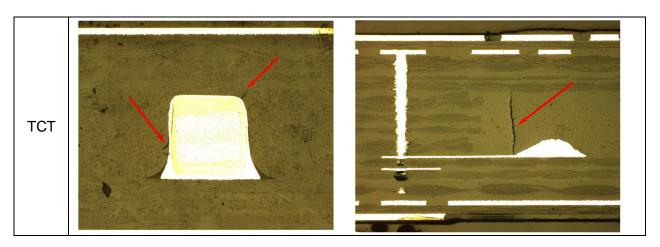

Nach den Umweltbelastungen alle Proben werden in Einbettungsstelle geschliffen und unter Mikroskop analysiert und ausgewertet. Tabelle 6 zeigt alle Ergebnisse. Einzelschliffbilder sind in Abbildung 20, 21, 22 dargestellt.

Alle Proben haben die MSL3 und HTSL Teste bestanden. Bei TCT Test zeigt leichte Rissbildung im reinen Harzbereich um passive Bauelemente (Abbildung 22). Der Grund dafür war, dass im reinen Harzbereich das Material keine mechanische Unterstützung von Glasgewerbe vorhanden ist und bei den Temperaturzyklen sich stark ausdehnt oder schrumpft. Für Aufbau der Vorfeldleiterplatte wurde ein FR4 Material mit einer Tg von 170°C eingesetzt. Wenn die Testtemperatur je nah an Tg ist, desto größer wird der CTE-Wert, was

zu einer größeren Volumenänderung verursacht. Um dieses Problem umzugehen können für künftige Serienherstellung zwei Lösungen einsetzen:

- Reines (glasfaserfreies) Harzbereich zu reduzieren durch engere Dimensionsanpassung des FR4 Materials zu einzubettenden Bauteilen

- Einsatz vom FR4 Material mit noch höherem Tg-Wert

| Teste | Rissbildung in Flipchip Bereich | Rissbildung in passiven Bauelemente | Rissbildung in<br>Lötstelle |

|-------|---------------------------------|-------------------------------------|-----------------------------|

| MSL3  | nein                            | nein                                | nein                        |

| TCT   | nein                            | leicht, nicht delaminiert           | nein                        |

| HTSL  | nein                            | nein                                | nein                        |

Tabelle 6 Ergebnisse der Zuverlässigkeitsteste mit Vorfeldleiterplatten

Abbildung 20 Schliffuntersuchung von Vorfeldleiterplatten nach den jeweiligen Zuverlässigkeitstesten

Abbildung 21 Schliffuntersuchung von Lötstellen nach den jeweiligen Zuverlässigkeitstesten

Abbildung 22 Rissbildung im Reinharzbereich um einbettete passive Bauelementen nach den jeweiligen Zuverlässigkeitstesten

(Dieser Abschnitt wurde aus Geheimhaltungsgründen entnommen)

#### **Berichtsblatt**

| 1. ISBN oder ISSN<br>keine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Berichtsart (Schlussbericht oder Veröffentlichung)     Schlussbericht                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3. Titel Schlussbericht Projekt VoLiFa2020 (" <u>Vo</u> lladaptive Lichtverteilung für ei Förderkennzeichen: 13N13046                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ine intelligente, effiziente und sicher                                                                                                                                                                                                                                                                                                     | e <u>Fa</u> hrzeugbeleuchtung")                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4. Autor(en) [Name(n), Vorname(n)] 4a) sämtliche Autoren Bericht                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                             | 5. Abschlussdatum des Vorhabens<br>Juni 2017                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Jue Chen, Schweizer Electronic AG 4b) sämtliche Autoren Publikation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                             | 6. Veröffentlichungsdatum<br>geplant                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Thomas Gottwald, Schweizer Electronic AC Dirk Gennermann, Schweizer Electronic AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                             | 7. Form der Publikation Website                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8. Durchführende Institution(en) (Name, Ad<br>Schweizer Electronic AG, Einstein:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                             | 9. Ber. Nr. Durchführende Institution keine                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                             | 10. Förderkennzeichen<br>13N13046                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                             | 11. Seitenzahl<br>26                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12. Fördernde Institution (Name, Adresse)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                             | 13. Literaturangaben<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Bundesministerium für<br>Bildung und Forschung (BMBF)<br>53170 Bonn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                             | 14. Tabellen 6                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                             | 15. Abbildungen<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16. Zusätzliche Angaben<br>keine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17. Vorgelegt bei (Titel, Ort, Datum)<br>keine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| nebeneinander auf der Leiterplat Fahrzeugbeleuchtungssystems wi Display (LCD) als Blendenelemei Leistungsdichte des hochkomple Standardleiterplattenlösung zu erfü Ein neuer Ansatz, basierend auf passiven Bauelementen mittels Standardleiterplattenlösung zu erfü Ein neuer Ansatz, basierend auf passiven Bauelementen mittels Standick Embedding Technologie (i² EAVT durch Flipchip gemeinsam anschließend in die Leiterplatte ei Bauraumproblem und lass sich thermischen und elektrischen Perfolm Projekt konnte die Logik Embesscheinwerfersystem weiter entwi Entwicklungen. Mit der im Projes Serienproduktion den Markteintritt 19. Schlagwörter | der direkten Einbettung von ungel Standardleiterplattenprozesses, wur Board®) von SCHWEIZER wurden mit passiven Bauelementen auf ingebettet. Die hergestellte hochkor weiteren Vorteilen beim Design, in ormance, was durch den Stand der edding Technologie für Hochtempel ckelt werden und bilden die Basekt aufgebauten Lieferkette kann | eines intelligenten, volladaptiven einem integrierten Flüssigkristallnde Elektronik und die steigende die Bauraumanforderungen mit häusten Halbleiterbausteinen und de entwickelt. Basierend auf der Halbleiter mittels einer geeigneten einem Interposer bestückt und mpakte Leiterplatte löst damit das n der Zuverlässigkeit und in der Technik kaum möglich wäre. raturanwendungen, wie z.B. LED is für weitere kundenspezifische SCHWEIZER für die zukünftige |

| 20. Verlag<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                             | 21. Preis 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### **Document Control Sheet**

| 1. ISBN or ISSN<br>none                                                                                                                               | 2. type of document (e.g. report, publication) Report |                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------|

| 3. title Report Project VoLiFa2020 – ("Volladaptive Lichtverteilung für ei Förderkennzeichen: 13N13046                                                | ine intelligente, effiziente und sicher               | e <u>Fa</u> hrzeugbeleuchtung") |

| 4. author(s) (family name, first name(s)) 4a) Authors Report                                                                                          |                                                       | 5. end of project<br>June 2017  |

| Jue Chen, Schweizer Electronic AG 4b) sämtliche Autoren Publikation Thomas Gottwald, Schweizer Electronic AG Dirk Gennermann, Schweizer Electronic AG |                                                       | 6. publication date planned     |

|                                                                                                                                                       |                                                       | 7. form of publication Website  |

| 8. performing organization(s) (name, address) Schweizer Electronic AG, Einsteinstraße 10, 78713 Schramberg                                            |                                                       | 9. originator's report no. none |

|                                                                                                                                                       |                                                       | 10. reference no.<br>13N13046   |

|                                                                                                                                                       |                                                       | 11. no. of pages<br>26          |

| 12. sponsoring agency (name, address)  Bundesministerium für                                                                                          |                                                       | 13. no. of references<br>0      |

| Bildung und Forschung (BMBF) 53170 Bonn                                                                                                               |                                                       | 14. no. of tables               |

|                                                                                                                                                       |                                                       | 15. no. of figures 24           |

| 16. supplementary notes none                                                                                                                          |                                                       |                                 |

| 17. presented at (title, place, date) none                                                                                                            |                                                       |                                 |

#### 18. abstract

Today the semiconductor devices in headlight system of cars are normally as discrete package assembled on PCBs. By the development of an intelligent and full adaptive automotive headlight system, the solid light devices of LEDs (light-emitting diode) were utilized as light source combined an integrated LCD (liquid crystal display). This system allows a well-defined and highly dynamic light distribution suited for every driving situation. Beside the complexity in optical and software system for technical realization there is another challenge, how all applied electronics with high power density install in limited room by using the standard PCB solution.

A new approach based on directly embedding of semiconductor and passive devices into PCB by using standard PCB manufacturing process was developed. This technology derived from SCHWEIZER's i² Board® of logic embedding, where the bare die was bumped with a proper interconnection material (Cu pillar) and assembled together with other passives of the periphery onto an FR4-interposer, subsequently. The assembled interposer was further laminated into the PCB. This hybrid embedded approach leads to miniaturization of PCB and presents supplementary benefits such as increased electrical and thermal performance, higher reliability, more design freedom, which are hardly possible by using standard PCB solution.

In this Project the embedding technology for high temperature applications in complex headlight system were developed. The function was verified by manufactured demonstrator. This provided a basis for further customer specific applications. Furthermore the complete supply chain was successfully built in the project which can reduce the hurdle of the market entry by transfer this technology to mass production in the future.

19. keywords

logic embedding, passive embedding, i² board technology, IC embedded pcb

| 20. publisher | 21. price |

|---------------|-----------|

| 0             | 0         |